目录

一、前言

二、Logic Level distribution

2.1 logic level配置

2.2 Logic Level Distribution报告

2.3 Logic Level 报告详情查看

2.4 Route Distributions 报告详情查看

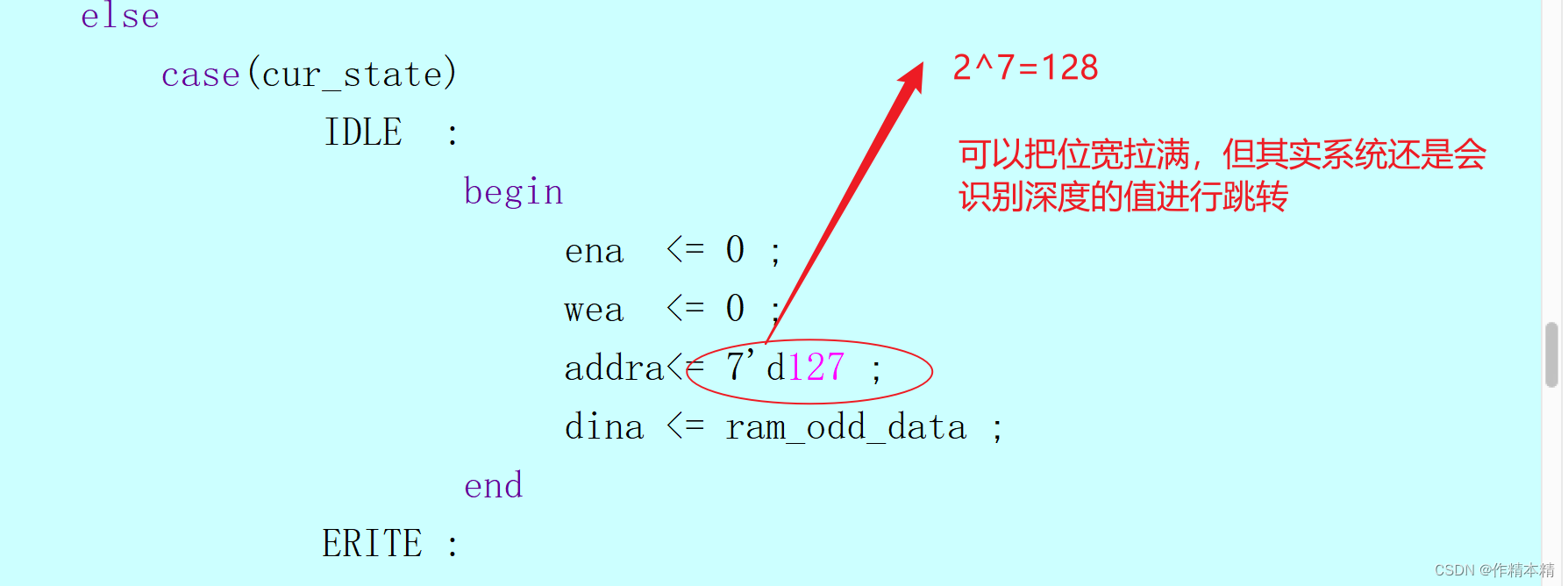

2.5 示例代码

一、前言

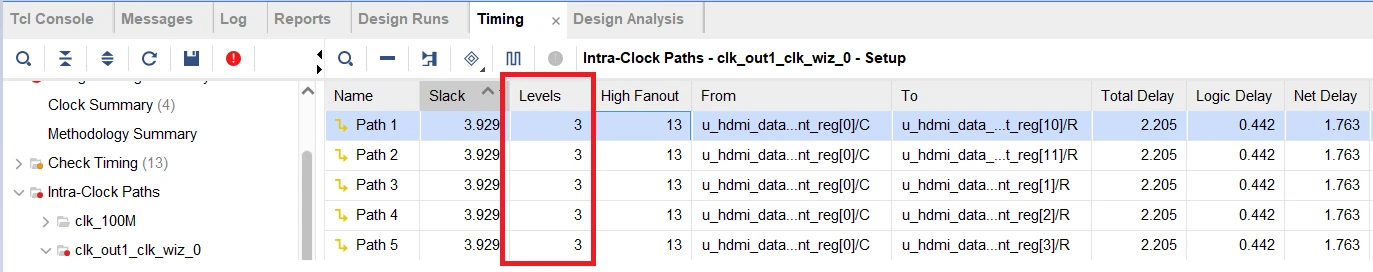

在工程设计中,如果需要了解路径的逻辑级数,可以在report timing summary中找到对应的时序路径,查看时序路径的详情报告中有逻辑级数的信息,如下图

这种方法查看有一个缺点,就是无法知道工程设计中逻辑级数的总体情况,这个时候就可以使用Report design analysis中的Include logic level distribution来查看

二、Logic Level distribution

2.1 logic level配置

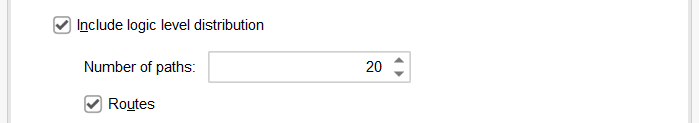

工程运行完Synthesize或implement时,进入菜单栏的“Reports”中,在“Reports->Report Design Analysis->Options”中,存在“Include logic level distribution”,默认不勾选,勾选后同时可以设置展示总的显示逻辑级数数量Number of paths,默认是1000条,表示最多只显示1000条,这1000条是所有路径中最差slack的1000条,不足1000条时按实际显示路径数显示。

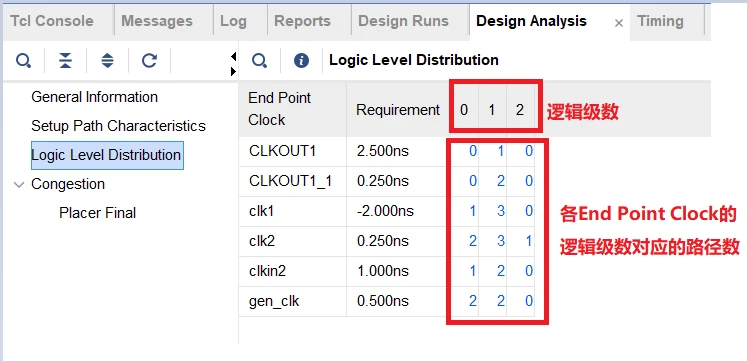

2.2 Logic Level Distribution报告

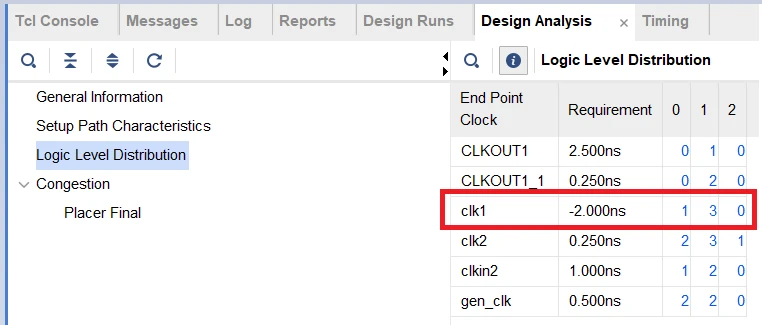

以Number of paths设置20为例,在Logic Level Distribution中将显示所有时序路径中最差的20条路径。注:logic level distribution只考虑setup路径。

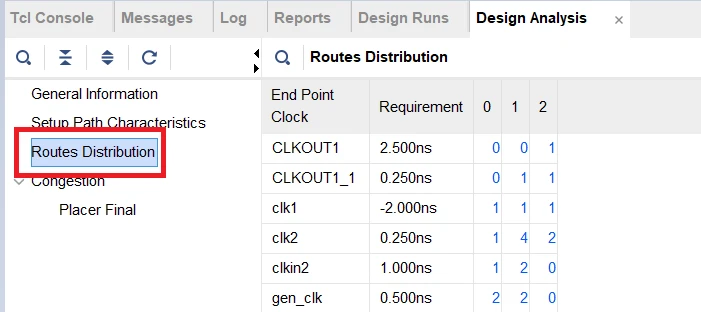

左侧报告包含3类内容:

End Point Clock:根据所有时序路径中End Point Clock来划分

Requirement:展示的End point clock对应路径中最差的Requirement,以End point clock为clk1,逻辑级数为0的1条,逻辑级数为1的3条,逻辑级数为2的没有

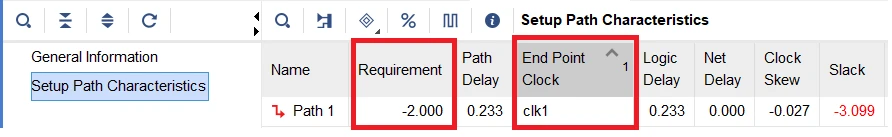

查看逻辑级数为0路径的requirement

查看逻辑级数为1路径的requirement,在Logic level distribution中clk1选取的requirement为-2,即为所有路径requirement中的最小值

工程中各逻辑级数:此处时序路径数逻辑级数只有0级,1级和2级,下面对应的展示了各逻辑级数的路径数量,所有路径数量加起来即为设置的Number of paths值20

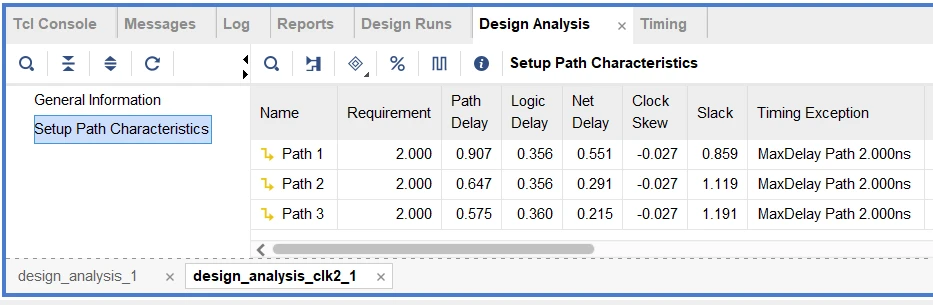

2.3 Logic Level 报告详情查看

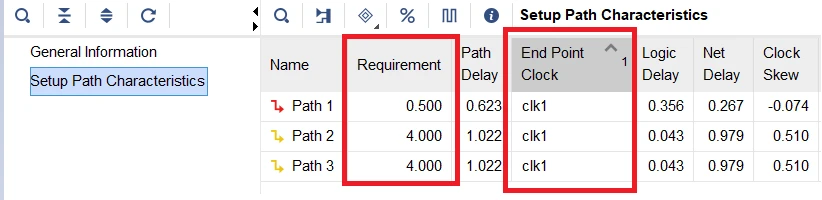

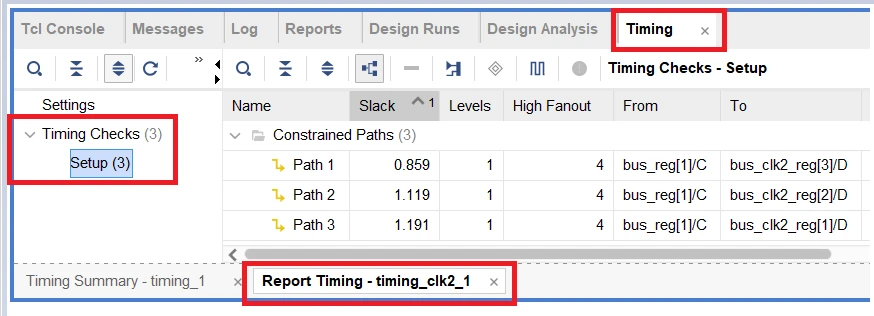

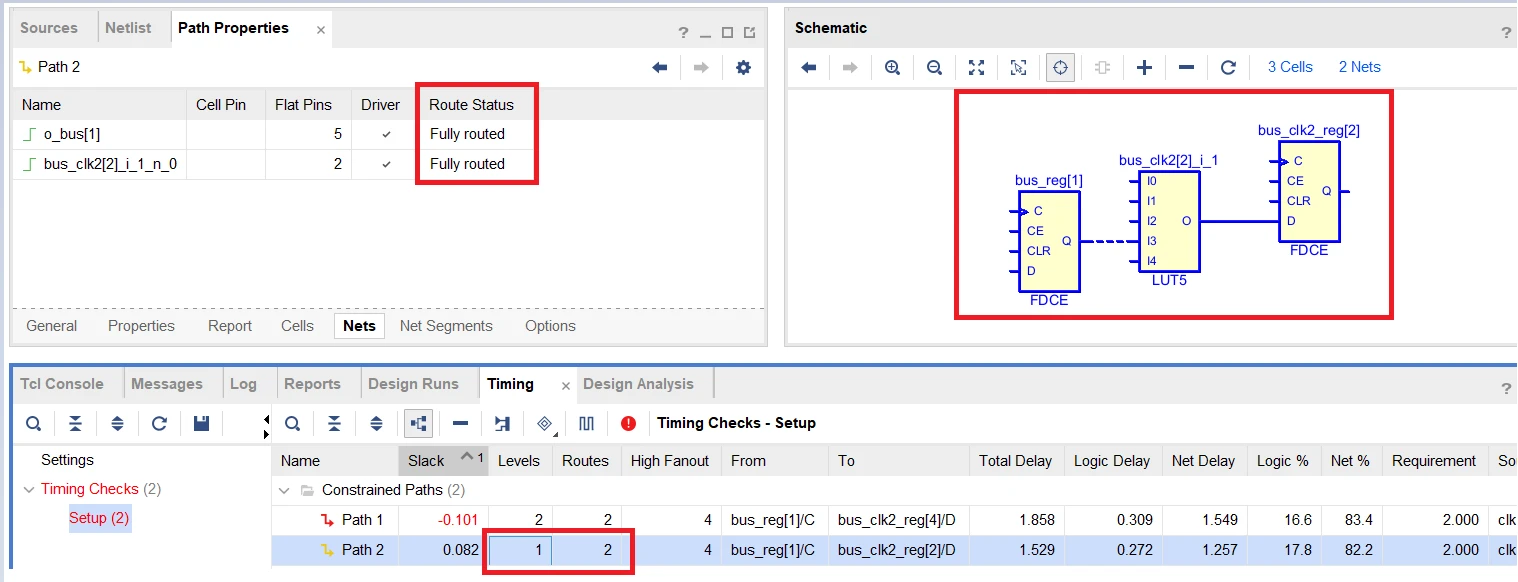

在logic level distribution报告中,选中需要查看的路径,以下图clk2的逻辑级数为1的3条路径为例,见红框内,点击鼠标左键,弹出弹框

选择“Report Design Analysis on Timing Paths”,在原有的Design analysis窗口中打开报告,报告为setup path characteristics

选择“Report Timing on Timing Paths”,在新打开的Timing窗口中以时序报告路径的形式展现

在完成Implement后,选择“Select Timing Paths”,将会在Netlist窗口和device中显示该路径中的包含的cells和路径(白色高亮)

2.4 Route Distributions 报告详情查看

生成Report Design Analysis时如果勾选Routes,则可以生成Route Distributions报告,主要提供时序路径中完全布线的net数量

Routes数量表示时序路径上data path中属于fully routed的net数量,通常是和逻辑级数一致,如果时序路径属于起点或终点为port的,如recovery路径或设置了setup_output_delay的路径,则logic level值和routes会不一致

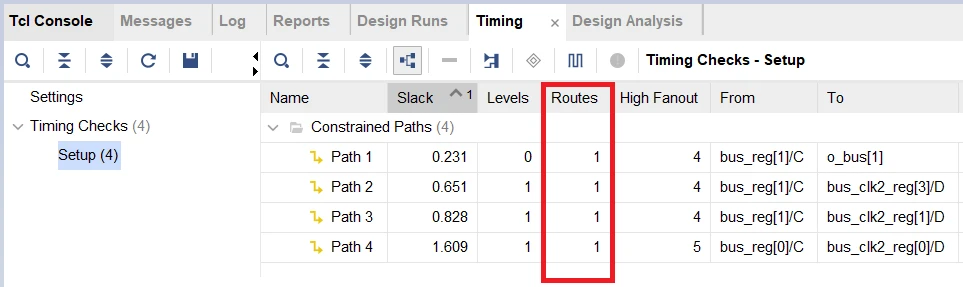

以上图的end point clock为clk2,数量为1的4为例,执行report timing on timing paths,时序报告中有一列Routes,显示了对应路径 routes的数量,图中都为1

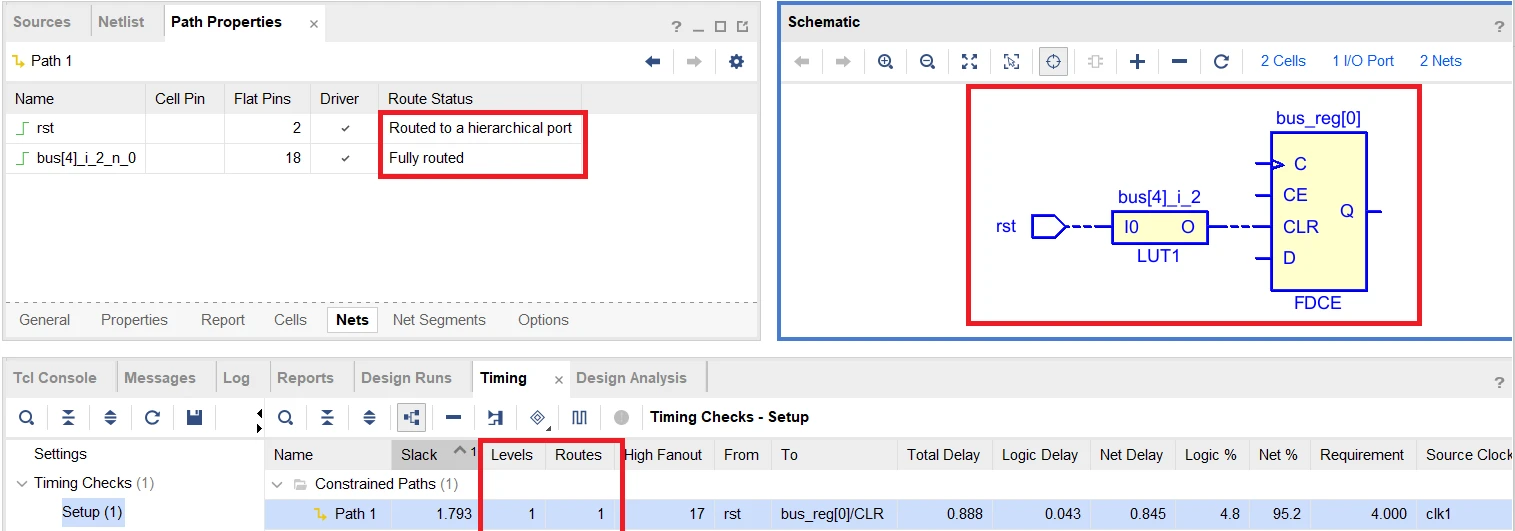

执行select timing paths,在Net窗口会显示对应的routes名称,Route Status为Fully routed的才被考虑,如下图第1条net rst属于routed to a hierarchical port,则不会考虑进Routes Distribution中,因此路径的routes数量为1,level也为1。

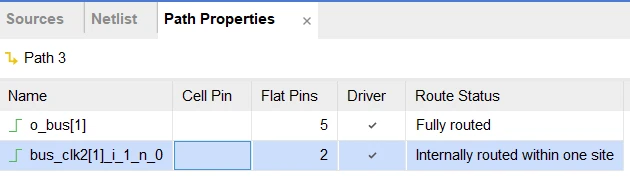

Route Status为internally routed within one site也不会被统计到routes中

下面的路径中logic level为1,route数量为2

2.5 示例代码

module logic_level(CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,CLKFBOUT,clk1,clk2,rst,d1,d2,S,i_bus,o_bus,bus_clk2,out_syn,out_asyn,and_out,o_case);

input CLKIN1,CLKIN2,CLKINSEL,CLKFBIN,clk1,clk2,rst,d1,d2,S;

input [4:0] i_bus;

output reg [4:0] o_bus,bus_clk2;

output out_syn,out_asyn,and_out,CLKFBOUT;

reg ff1,ff2,ff_asyn,ff_syn,ff_and;

reg ff_case;

output reg o_case;

reg [4:0] bus;

wire sum12,and_c,CLKOUT0,CLKOUT1;

wire [4:0] bus_c;

wire o_bufgmux,ffcase_n;

PLLE2_ADV #(

.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW

.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64)

.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB, (-360.000-360.000).

// CLKIN_PERIOD: Input clock period in nS to ps resolution (i.e. 33.333 is 30 MHz).

.CLKIN1_PERIOD(0.0),

.CLKIN2_PERIOD(0.0),

// CLKOUT0_DIVIDE - CLKOUT5_DIVIDE: Divide amount for CLKOUT (1-128)

.CLKOUT0_DIVIDE(1),

.CLKOUT1_DIVIDE(2),

.CLKOUT2_DIVIDE(4),

.CLKOUT3_DIVIDE(5),

.CLKOUT4_DIVIDE(1),

.CLKOUT5_DIVIDE(1),

// CLKOUT0_DUTY_CYCLE - CLKOUT5_DUTY_CYCLE: Duty cycle for CLKOUT outputs (0.001-0.999).

.CLKOUT0_DUTY_CYCLE(0.4),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT2_DUTY_CYCLE(0.5),

.CLKOUT3_DUTY_CYCLE(0.5),

.CLKOUT4_DUTY_CYCLE(0.5),

.CLKOUT5_DUTY_CYCLE(0.5),

// CLKOUT0_PHASE - CLKOUT5_PHASE: Phase offset for CLKOUT outputs (-360.000-360.000).

.CLKOUT0_PHASE(0.0),

.CLKOUT1_PHASE(0.0),

.CLKOUT2_PHASE(0.0),

.CLKOUT3_PHASE(0.0),

.CLKOUT4_PHASE(0.0),

.CLKOUT5_PHASE(0.0),

.COMPENSATION("EXTERNAL"), // ZHOLD, BUF_IN, EXTERNAL, INTERNAL

.DIVCLK_DIVIDE(1), // Master division value (1-56)

// REF_JITTER: Reference input jitter in UI (0.000-0.999).

.REF_JITTER1(0.0),

.REF_JITTER2(0.0),

.STARTUP_WAIT("FALSE") // Delay DONE until PLL Locks, ("TRUE"/"FALSE")

)

PLLE2_ADV_inst (

// Clock Outputs: 1-bit (each) output: User configurable clock outputs

.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0

.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1

.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2

// Feedback Clocks: 1-bit (each) output: Clock feedback ports

.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock

// Clock Inputs: 1-bit (each) input: Clock inputs

.CLKIN1(CLKIN1), // 1-bit input: Primary clock

.CLKIN2(CLKIN2), // 1-bit input: Secondary clock

// Control Ports: 1-bit (each) input: PLL control ports

.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2

.RST(rst), // 1-bit input: Reset

// Feedback Clocks: 1-bit (each) input: Clock feedback ports

.CLKFBIN(CLKFBIN) // 1-bit input: Feedback clock

);

// End of PLLE2_ADV_inst instantiation

always@(posedge CLKOUT0,negedge rst)

if(!rst)

begin

ff1<=1'b0;

ff2<=1'b0;

end

else begin

ff1<=d1;

ff2<=d2;

end

assign sum12=ff1+ff2;

always@(posedge CLKOUT1,negedge rst)

if(!rst)

ff_syn<=1'b0;

else begin

ff_syn<=sum12;

end

assign out_syn=ff_syn;

always@(posedge clk1,negedge rst)

if(!rst)

ff_asyn<=1'b0;

else begin

ff_asyn<=sum12;

end

assign out_asyn=ff_asyn;

assign and_c=ff_asyn&d1;

always@(posedge clk1,negedge rst)

if(!rst)

ff_and<=1'b0;

else begin

ff_and<=and_c;

end

assign and_out=ff_and;

always@(posedge clk1,negedge rst)

if(!rst)

bus<=5'b0;

else begin

bus<=i_bus+1'b1;

end

assign bus_c=bus+d2;

always@(*)

begin

o_bus=bus;

end

always@(posedge clk2,negedge rst)

if(!rst)

bus_clk2<=5'b0;

else begin

bus_clk2<=bus_c+d1;

end

//set_case_analysis

BUFGMUX #(

)

BUFGMUX_inst (

.O(o_bufgmux), // 1-bit output: Clock output

.I0(CLKIN1), // 1-bit input: Clock input (S=0)

.I1(CLKIN2), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

always@(posedge o_bufgmux,negedge rst)

if(!rst)

ff_case<=1'b0;

else begin

ff_case<=d1;

end

assign ffcase_n=!ff_case;

always@(posedge o_bufgmux,negedge rst)

if(!rst)

o_case<=1'b0;

else begin

o_case<=ffcase_n;

end

endmodule 约束

//创建主时钟和生成时钟

create_clock -period 10.000 -name clkin1 -waveform {0.000 5.000} -add [get_ports CLKIN1]

create_clock -period 5.000 -name clkin2 -waveform {0.000 2.500} -add [get_nets CLKIN2]

create_clock -period 4.000 -name clk2 -waveform {0.000 2.000} -add [get_ports clk2]

create_clock -period 4.000 -name clk1 -waveform {0.000 2.000} -add [get_ports clk1]

create_generated_clock -name gen_clk -source [get_pins PLLE2_ADV_inst/CLKOUT1] -multiply_by 2 -add -master_clock clkin2 [get_pins PLLE2_ADV_inst/CLKOUT0]

set_input_jitter [get_clocks clk2] 0.500

set_clock_latency -clock [get_clocks clk2] 0.333 [get_pins {bus_reg[1]/D}]

set_system_jitter 0.009

set_clock_uncertainty 0.500 [get_clocks clk1]

//设置时钟组和总线偏斜

set_clock_groups -name clkin1_group -asynchronous -group [get_clocks clkin1]

set_bus_skew -from [get_cells {{bus_reg[0]} {bus_reg[1]} {bus_reg[2]} {bus_reg[3]} {bus_reg[4]}}] -to [get_cells {{bus_clk2_reg[0]} {bus_clk2_reg[1]} {bus_clk2_reg[2]} {bus_clk2_reg[3]} {bus_clk2_reg[4]}}] 0.550

set_input_delay -clock [get_clocks clk1] 1.111 [get_ports {d1 d2 {i_bus[0]} {i_bus[1]} {i_bus[2]} {i_bus[3]} {i_bus[4]} rst}]

set_output_delay -clock [get_clocks clk2] 0.222 [get_ports {and_out {o_bus[0]} {o_bus[1]} {o_bus[2]} {o_bus[3]} {o_bus[4]} out_asyn out_syn}]

//设置时序例外分析

set_false_path -setup -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_clk2_reg[4]/D}]

set_max_delay -from [get_pins {bus_reg[1]/C}] 2.000

set_min_delay -from [get_pins {bus_reg[0]/C}] 0.500

set_external_delay -from [get_ports CLKFBOUT] -to [get_ports CLKFBIN] 0.444

set_multicycle_path -from [get_pins {bus_reg[0]/C}] -to [get_pins {bus_clk2_reg[2]/D}] 2

set_disable_timing [get_cells {bus_reg[3]}]

//设置时序断言

set_case_analysis 1 [get_ports S]

set_data_check -from [get_pins {bus_reg[2]/C}] -to [get_pins {bus_reg[2]/Q}] 0.333 -clock [get_clocks clk2]

set_clock_sense -positive -clocks [get_clocks clk1] [get_pins ff_asyn_reg/C]

group_path -name {group_path} -weight 1.000 -from [get_ports {d1 d2}]